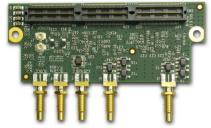

# XRM2-ADC-D9/500

Datasheet Revision: 2.0 1st November 2020

AD01252

# BUFFFR XRM2 Interface 8x HSSIO & 148 GPIO

## **Prime Application**

IF/Baseband Signal Sampling

# **Board Features**

- Dual 14-bit 500Msps ADCs

- External Clock Input

# Summary

The XRM-ADC-D9/500 is an XRM2 I/O Module, providing two Analog to Digital converters with 14-bit resolution at sampling rates up to 500Msps.

Aimed at IF/Baseband Signal Sampling, the sampling clock can be sourced from either an external clock source or from a clock generated within the attached FPGA board. An Auxiliary I/O port is provided for use as a trigger input and general purpose signaling. An additional two ports are available for use as high-speed interconnect between boards for synchronisation.

#### **Deliverables**

XRM2-ADC-D9/500 Board One Year Warranty One Year Technical Support

#### **Board Format**

Alpha Data XRM2 I/O Module

#### Input/Output Interfaces

#### ADC

**Dual Analog to Digital Converters**

Resolution: 14-bit

Max Sample Freq: 500Msps Bandwidth: 4.5MHz to 700MHz

Impedance: 50Ω Connector: SSMC

# **External clock input**

External Clock Input

# Auxiliary I/O

Auxiliary I/O

## Synchronisation I/O

Synchronisation I/O

# **Environmental Specification**

| Cooling<br>Option | Operating<br>Temperatures |       | Storage<br>Temperatures |       |

|-------------------|---------------------------|-------|-------------------------|-------|

|                   | Min                       | Max   | Min                     | Max   |

| AC0               | 0°C                       | +55°C | -40°C                   | +85°C |

#### **Operating Humidity**

Up to 95% (non-condensing)

# **EMC Standards**

FCC 47CFR Part 2

EN55022:2010 Equipment ClassB

**Ordering Information**

Order Code: XRM2-ADC-D9/500

Address: