Summary

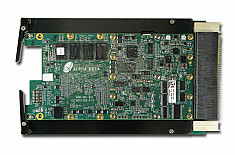

The XRM2-ADC-D10/250 is an XRM2 I/O Module, providing two Analog to Digital converters with 16-bit resolution at sampling rates up to 250Msps.

Aimed at IF/Baseband Signal Sampling, the sampling clock can be sourced from either an external clock source or from a clock generated within the attached FPGA board. An Auxiliary I/O port is provided for use as a trigger input and general purpose signaling. An additional two ports are available for use as high-speed interconnect between boards for synchronisation.

Applications

IF/Baseband Signal Sampling

Board Features

Dual 16-bit 250Msps ADCsExternal Clock Input