Summary

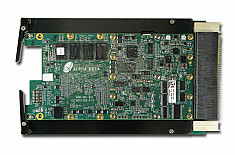

The XRM2-ADC-D3/1G5 is an XRM2 I/O Module, providing two Analog to Digital converters with 8-bit resolution and sampling rates up to 1.5Gsps.

Aimed at IF/Baseband Signal Sampling, the sampling clock can be sourced from either an external clock source or from a clock generated within the attached FPGA board. An Auxiliary I/O port is provided for use as a trigger control or for general purpose signaling.An additional two ports are available for use as high-speed interconnect between boards for synchronisation.

The XRM2-ADC-D3/1G5 is based around the ADC08D1500 by National Semiconductors. A built-in thermal monitor allows the user to check the operating temperature of the ADC. Provided as part of the sample design is the functionality to read the temperature of the device, and software to monitor this and recalibrate the ADC if the thermal drift is sufficient. The software will also shut the ADC down if the device starts to go over the maximum operating temperature.

Applications

IF/Baseband Signal Sampling

Board Features

Dual 8-bit 1.5Gsps ADCsExternal Clock Input

Thermal monitoring of the ADCs