Summary

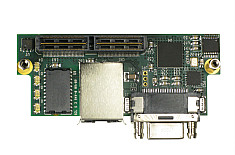

The ADM-XRC-KU1 is a high performance reconfigurable XMC (compliant to VITA Standard 42.0 and 42.3) based on the AMD Kintex Ultrascale range of Platform FPGAs.

Features include PCI Express Gen2 interface, external memory, high density I/O, system monitoring and flash boot facilities.

A comprehensive cross platform API with support for Microsoft Windows, Linux and VxWorks provides access to the full functionality of these hardware features.

Board management is provided by the combination of the Artix FPGA and AVR Microcontroller. This allows the board to be managed via PCI Express or via USB.

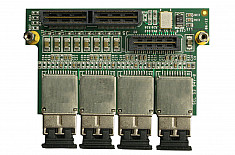

The KU1 provides multiple communications modes:

PCI Express Gen2 x4 through the Artix FPGA with an optional Gen3 x4 PCI Express link direct to the target FPGA.

Gen3 x8 PCI Express link direct to the target when the bridge is in USB mode.

An optional Gen3 x8 PCI Express link provided through Pn6 using a compatible XMC carrier.

Applications

Embedded Data Processing

Radar/Sonar Beamforming

ELINT

Image/Video Processing

Digital Signal Processing

Data Encryption

Board Features

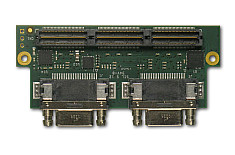

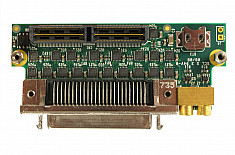

Air-Cooled/Conduction-Cooled OptionsSeparate PCI Express Bridge

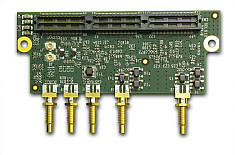

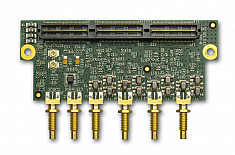

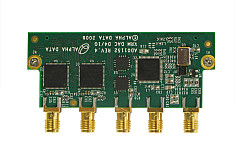

XRM2 I/O Interface